世界上首個具有自對準柵極的疊層垂直納米環柵晶體管的實現

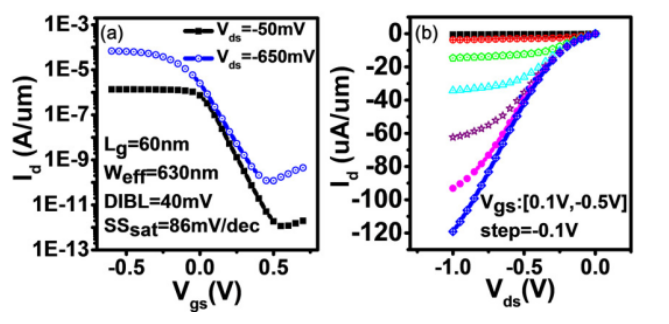

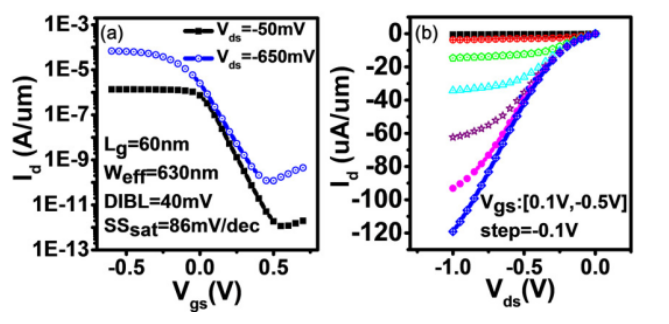

從Intel首發22nm FinFET工藝之后,全球主要的半導體廠商在22/16/14nm節點開始啟用FinFET鰭式晶體管,目前全球最先進的半導體工藝已經進入7nm,下一步還要進入5nm、3nm節點,制造難度越來越大,其中晶體管結構的限制至關重要,未來的工藝需要新型晶體管。三星在去年率先宣布3nm節點改用GAA環繞柵極晶體管。基于全新的GAA晶體管結構,三星通過使用納米片設備制造出了MBCFET(Multi-Bridge-Channel FET,多橋-通道場效應管),該技術可以顯著增強晶體管性能,主要取代FinFET晶體管技術。基于上述信息也可以看出GAA環繞柵極晶體管的重要意義。這里,朱慧瓏課題組系統地研發了一種原子層選擇性刻蝕鍺硅的方法,結合多層外延生長技術將此方法用于鍺硅/硅超晶格疊層的選擇性刻蝕,從而精確地控制納米晶體管溝道尺寸和有效柵長,首次實現了垂直納米環柵晶體管的自對準高k金屬柵后柵工藝。其集成工藝與主流先進CMOS制程兼容。所獲得的柵長約60 nm,納米片厚度20 nm的p型VSAFET。原型器件的SS、DIBL和電流開關比(Ion/Ioff)分別為86 mV/dec、40 mV和1.8x105。

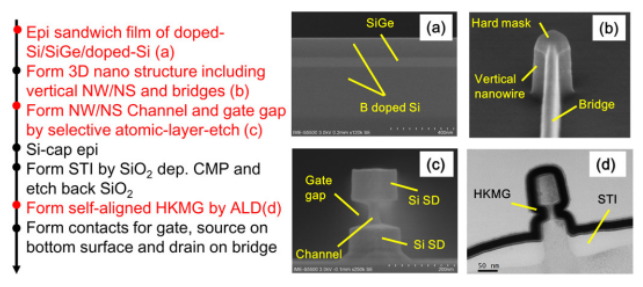

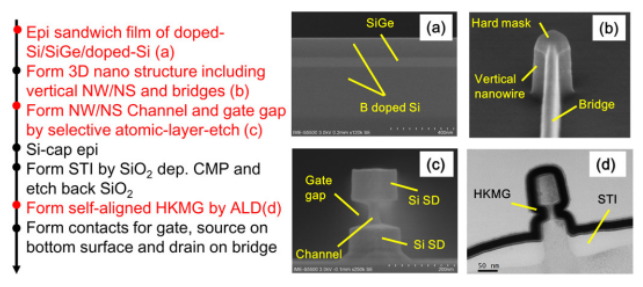

Figure 1. VSAFETs的工藝流程。(a)Si/SiGe/Si之后的SEM圖,(b)RIE之后的3D結構SEM圖,(c)qALE之后的SEM圖,(d)HKMG沉積后的TEM圖。

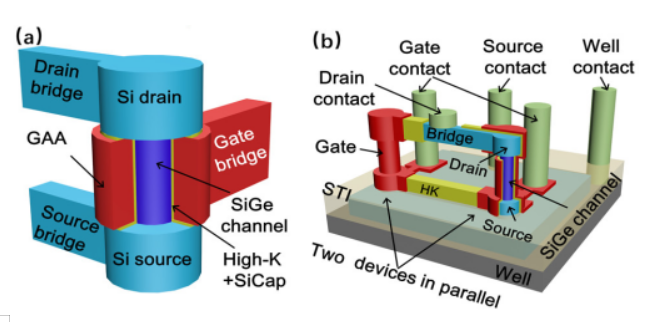

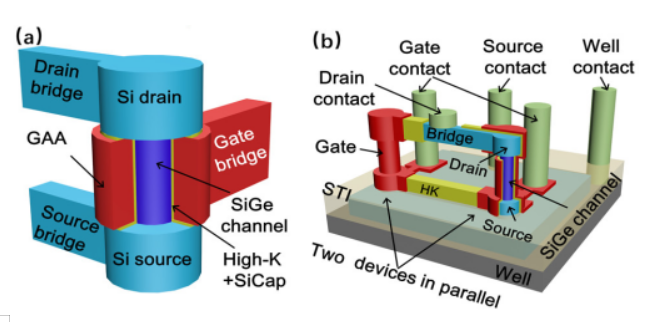

Figure 2. VSAFETs的原理示意圖。(a)單個裝置的結構設計,(b)兩個裝置串聯連接的的測試結構。

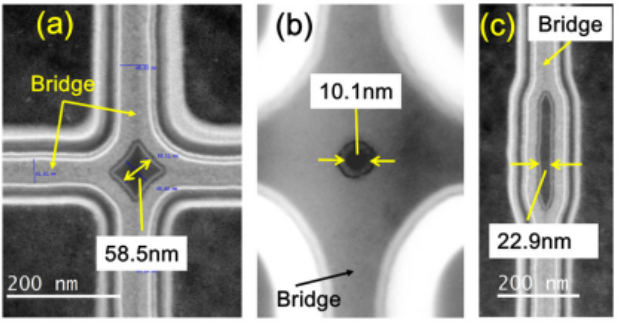

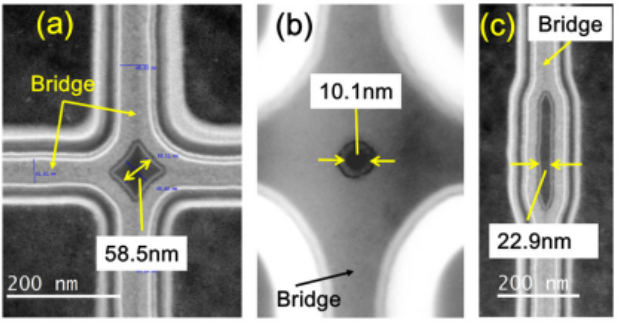

Figure 3. 配有包覆HKMG的VSAFETs的STEM頂視圖。(a)方形橫截面納米線,(b)圓形橫截面納米線,(c)納米片。

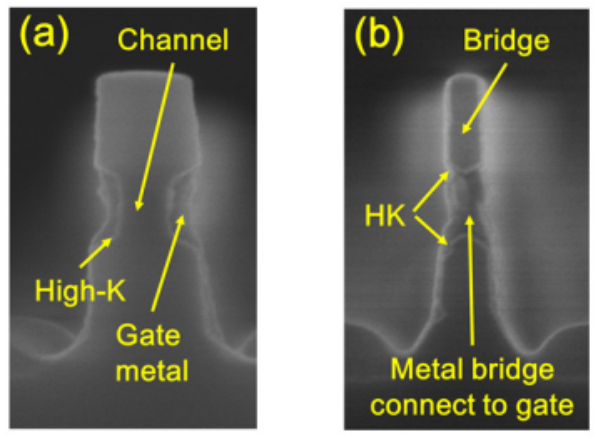

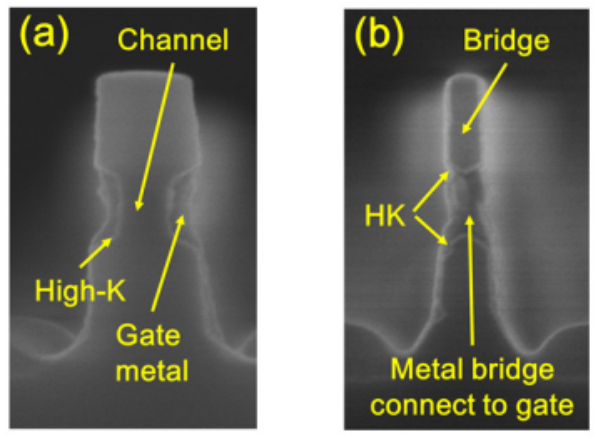

Figure 4.柵極金屬在活性離子刻蝕后(RIE),(a)VSAFETs的SEM圖:納米片裝置的HKMG和(b)與柵極的局部連接。

Figure 5.(a)pVSAFETs器件的結構和I-V特性,(a)轉移特性曲線和(b)輸出特性曲線。

該研究工作由中科院微電子所先導中心朱慧瓏研究員課題組于2019年發表在國際微電子器件領域的頂級期刊《IEEE Electron Device Letters》上。原文:Vertical Sandwich Gate-All-Around Field-Effect Transistors with Self-Aligned High-k Metal Gates and Small Effective-Gate-Length Variatio(DOI: 10.1109/LED.2019.2954537)